## Time-predictable Execution of Embedded Software on Multi-core Platforms

### SUDIPTA CHATTOPADHYAY M.ENG(HONS), INDIAN INSTITUTE OF SCIENCE, BANGALORE

A THESIS SUBMITTED

FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN COMPUTER SCIENCE

DEPARTMENT OF COMPUTER SCIENCE NATIONAL UNIVERSITY OF SINGAPORE 2012

# Declaration

I hereby declare that this thesis is my original work and it has been written by me in its entirety. I have duly acknowledged all the sources of information which have been used in the thesis. This thesis has also not been submitted for any degree in any university previously.

> SUDIPTA CHATTOPADHYAY 14th September, 2012

# Acknowledgements

First and foremost, I want to thank my advisor Prof. Abhik Roychoudhury for his generous guidance throughout my graduate studies. If this dissertation has taken any shape, it is due to his continuous and timely feedback on my research. I have thoroughly enjoyed all the technical discussions we have made in these four years. The quality of his guidance was way beyond my expectations. His long-term vision on research has entirely changed my viewpoint to evaluate certain aspects of research. If I ever get an opportunity to guide students, I wish that I can acquire some of his qualities to share.

I sincerely thank Prof. Khoo Siau Cheng for his teaching in the Program Analysis course. Before starting my graduate studies, I never took any course on program analysis. This dissertation revolves around designing several program analysis techniques. I truly believe that the course has built some solid foundation for me. Such a foundation on the basics of several program analysis methodologies has helped me throughout the work carried out in this dissertation.

My sincere thanks to Prof. Tulika Mitra for her research collaborations. I thank Prof. Wong Weng Fai and Prof. Liang Zhenkai for taking their time to be in my dissertation panel. I sincerely thank them for their feedback on this dissertation and helping me find some exciting directions to work in future. I thank Prof. Wang Yi from Uppsala University for his time to read my dissertation and his generous feedback.

I had a great opportunity to work with my fellow researchers in TU Dortmund, Germany. I am extremely grateful to Timon Kelter, Prof. Heiko Falk and Prof. Peter Marwedel for their excellent research collaborations. I wish to continue such collaborations for many more years in future. Finally, my sincere thanks to Lee Kee Chong for being an excellent partner in research collaborations.

It is the time to acknowledge my friends. My special thanks go to Hoang Nguyen, Shuang Liu and Sucheendra Kumar (Suchee), who are my great friends in daily life. I have bugged them with my meaningless talking and countless arguments. However, they have always been so nice to listen to me carefully and with a lot of patience. I take this opportunity to wish them best for their future endeavor. Besides, I really appreciate the support from my friends inside and outside the lab, including Dawei, Chundong, Lee Kee, Abhijeet, Marcele, Huping, Lavanya, Pooja, Tushar, Sun Tao, Richard, Ju Lei, Eric Liang, Thuan, Chen Liang, Mihai, Malai, Bodhi, Manoranjan, Manjunath, Sriganesh and Padmanabha. I also thank my long-time friends outside NUS, specifically, Deepak Vankadaru, Raveendra Holla, Satyajit, Sayan, Debashis, Subhadeep, Arnab, Abhinav, Sarasij and Abhijit.

I thank Srivatsan Raghavan, who was my mentor and a great friend in Synopsys. Even though he was my mentor in Synopsys, he had always inspired me to pursue higher studies. Besides, I thank my friends Gaurav and Vinod with whom I had worked very closely. I wish all of them very best for their future career.

I thank School of Computing for supporting me in my conference trips. I thank all the staffs in Dean's office, specifically, Ms. Loo Line Fong, Ms. Agnes Ang and Mr. Mark Christopher for helping me in several administrative matters.

My deepest gratitude to my parents and my family. They have been always supportive throughout my graduate studies.

In this last paragraph, I shall follow the usual standard of dedicating this dissertation to one of the most important persons in my life. Throughout my academic career, my true inspiration has been my uncle, who is also my first teacher (Jagabandhu aka "Gajai"). He is the one with whom I first stepped into the academic world, even before entering any primary school. He is my first mentor. Besides, his relentless struggle in life has given me enough mental strength to survive the difficult times in my graduate studies. Over the past two decades I have seen his struggles and it has helped me learn only one thing – the importance of being indifferent towards sorrow and happiness. Probably this is the last time I shall get an open opportunity to express my deepest gratitude towards him and I do this by dedicating this dissertation to him.

# Contents

|   | Dec  | laration                                        | i   |

|---|------|-------------------------------------------------|-----|

|   | Ack  | nowledgements                                   | ii  |

|   | Con  | tents                                           | iv  |

|   | Abs  | tract                                           | ix  |

|   | Rela | ated Publications                               | xi  |

|   | List | of Tables                                       | xi  |

|   | List | of Figures                                      | xii |

| 1 | Intr | oduction                                        | 1   |

|   | 1.1  | Real-time embedded systems                      | 1   |

|   |      | 1.1.1 Analysis of hard real-time systems        | 2   |

|   |      | 1.1.2 Can we use software testing to find WCET? | 4   |

|   | 1.2  | Motivation and thesis overview                  | 6   |

|   | 1.3  | Organization of the chapters                    | 7   |

| 2 | WC   | ET Analysis Background                          | 8   |

|   | 2.1  | Static WCET analysis                            | 8   |

|   | 2.2  | Example                                         | 13  |

|   | 2.3  | Chapter summary                                 | 14  |

| 3 | Lite | rature Review                                   | 15  |

|   | 3.1  | Cache analysis of a single task                 | 15  |

|   | 3.2  | Inter-task cache conflict analysis              | 16  |

|   | 3.3  | Shared cache analysis                                       |    |    |  |

|---|------|-------------------------------------------------------------|----|----|--|

|   | 3.4  | Shared bus modeling                                         |    | 20 |  |

|   | 3.5  | Time predictable micro-architecture and execution model     |    | 21 |  |

|   | 3.6  | Memory optimization for execution time predictability       |    | 21 |  |

|   |      | 3.6.1 Cache locking and cache partitioning                  |    | 21 |  |

|   |      | 3.6.2 Changing layout of memory blocks                      |    | 22 |  |

|   |      | 3.6.3 Scratchpad memory                                     |    | 23 |  |

|   |      | 3.6.4 Scratchpad allocation techniques                      |    | 24 |  |

| 4 | Unif | ed Cache Modeling for WCET Analysis and Layout Optimization | 15 | 26 |  |

|   | 4.1  | Technical Contributions                                     |    | 26 |  |

|   | 4.2  | Assumptions                                                 |    | 27 |  |

|   | 4.3  | Overview of our cache analysis                              |    | 27 |  |

|   | 4.4  | Details of Cache Analysis                                   |    | 30 |  |

|   | 4.5  | Analysis results                                            |    | 34 |  |

|   | 4.6  | WCET-centric code and data layout                           |    | 38 |  |

|   | 4.7  | Chapter Summary                                             |    | 43 |  |

| 5 | Mod  | leling Shared Cache for Timing Analysis                     |    | 44 |  |

|   | 5.1  | Introduction                                                |    | 44 |  |

|   | 5.2  | A background on existing cache analysis                     |    | 47 |  |

|   | 5.3  | Our proposed analysis framework                             |    | 48 |  |

|   |      | 5.3.1 General framework                                     |    | 48 |  |

|   |      | 5.3.2 A general code transformation framework               |    | 50 |  |

|   |      | 5.3.3 Refinement of inter-core cache conflicts              |    | 51 |  |

|   |      | 5.3.4 An extension to a generic cache analysis framework    |    | 53 |  |

|   |      | 5.3.5 Optimizations                                         |    | 53 |  |

|   | 5.4  | Implementation and evaluation using CBMC                    |    | 54 |  |

|   |      | 5.4.1 Implementation                                        |    | 54 |  |

|   |      | 5.4.2 Experimental setup                                    |    | 56 |  |

|   |      | 5.4.3 Evaluation                                            |    | 57 |  |

|   | 5.5  | Cache conflict refinement through symbolic execution        |    | 59 |  |

|   |      | 5.5.1 KLEE symbolic execution engine                        |    | 60 |  |

|   |            | 5.5.2 Cache conflict refinement                         | 62         |

|---|------------|---------------------------------------------------------|------------|

|   | 5.6        | Implementation and evaluation using KLEE                | 63         |

|   |            | 5.6.1 Implementation                                    | 63         |

|   |            | 5.6.2 Evaluation                                        | 64         |

|   |            | 5.6.3 Discussion                                        | 67         |

|   | 5.7        | Chapter summary                                         | 67         |

| 6 | Mod        | leling Shared Cache and Bus for Timing Analysis         | 69         |

|   | 6.1        | System and Architectural Model                          | 69         |

|   | 6.2        | Overview                                                | 71         |

|   | 6.3        | Bus aware WCET analysis                                 | 74         |

|   |            | 6.3.1 WCRT Estimation                                   | 79         |

|   | 6.4        | Experimental evaluation                                 | 82         |

|   | 6.5        | Extensions                                              | 87         |

|   | 6.6        | Chapter summary                                         | 89         |

| 7 | A U        | nified WCET Analysis Framework for Multi-core Platforms | 90         |

|   | 7.1        | Introduction                                            | 90         |

|   | 7.2        | Background                                              | 92         |

|   | 7.3        | Overview of our analysis                                | 93         |

|   | 7.4        | Interaction of shared resources with pipeline           | 95         |

|   |            | 7.4.1 Interaction of shared cache with pipeline         | 96         |

|   |            | 7.4.2 Interaction of shared bus with pipeline           | 96         |

|   | 7.5        | WCET computation under multiple bus contexts            | 99         |

|   |            | 7.5.1 Execution context of a basic block                | 99         |

|   |            | 7.5.2 Bounding the execution count of a bus context     | 101        |

|   | 7.6        | Effect of branch prediction                             | 105        |

|   |            | 7.6.1 Effect on cache for speculative execution         | 105        |

|   |            | 7.6.2 Effect on bus for speculative execution           | 106        |

|   |            |                                                         |            |

|   |            | 7.6.3 Computing the number of mispredicted branches     | 107        |

|   | 7.7        | 7.6.3 Computing the number of mispredicted branches     | 107<br>107 |

|   | 7.7<br>7.8 |                                                         |            |

|   |      | 7.8.2    | Detailed proofs                                                        | 109 |

|---|------|----------|------------------------------------------------------------------------|-----|

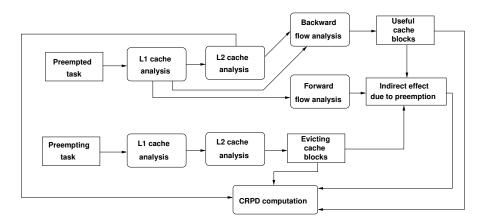

|   | 7.9  | Experin  | mental evaluation                                                      | 119 |

|   | 7.10 | Extensi  | ion of shared cache analysis                                           | 128 |

|   |      | 7.10.1   | Review of cache analysis for FIFO replacement                          | 129 |

|   |      | 7.10.2   | Analysis of shared cache with FIFO replacement                         | 130 |

|   |      | 7.10.3   | Interaction of FIFO cache with pipeline and branch predictor           | 131 |

|   |      | 7.10.4   | Experimental result                                                    | 131 |

|   |      | 7.10.5   | Other cache organizations                                              | 132 |

|   | 7.11 | Chapte   | r summary                                                              | 133 |

| 8 | Cacł | ne Relat | ed Preemption Delay Analysis for Shared Cache                          | 134 |

|   | 8.1  | Introdu  | ction                                                                  | 134 |

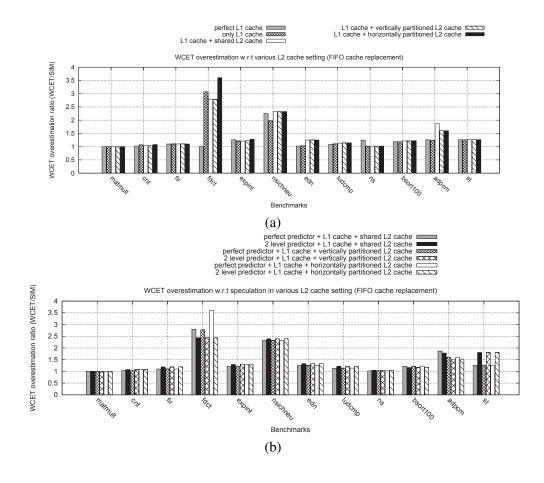

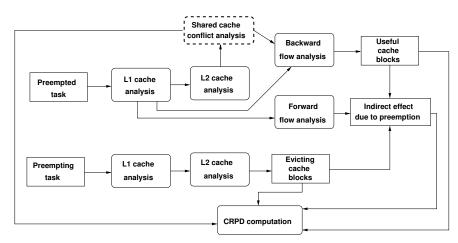

|   | 8.2  | Overvi   | ew of our analysis                                                     | 136 |

|   | 8.3  | CRPD     | Analysis                                                               | 141 |

|   |      | 8.3.1    | Flow Analysis                                                          | 142 |

|   |      | 8.3.2    | Preemption delay computation                                           | 147 |

|   |      | 8.3.3    | Handling shared caches in multi-cores                                  | 151 |

|   | 8.4  | Soundr   | ness of analysis                                                       | 152 |

|   |      | 8.4.1    | Detailed proofs                                                        | 153 |

|   | 8.5  | Extensi  | ion                                                                    | 163 |

|   | 8.6  | Experin  | mental evaluation                                                      | 164 |

|   | 8.7  | Chapte   | r summary                                                              | 170 |

| 9 | Mod  | eling Ca | ache Coherence for WCET Analysis                                       | 172 |

|   | 9.1  | Introdu  | ction                                                                  | 172 |

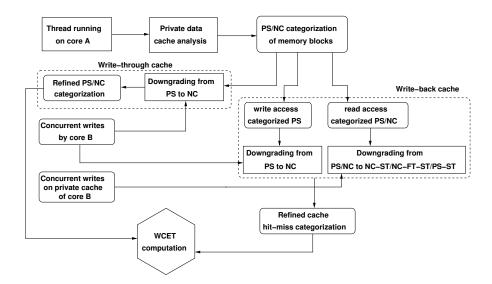

|   | 9.2  | Overvi   | ew                                                                     | 174 |

|   | 9.3  | Analys   | is                                                                     | 176 |

|   |      | 9.3.1    | Parallel programming model                                             | 177 |

|   |      | 9.3.2    | A review of scope based data cache analysis                            | 178 |

|   |      | 9.3.3    | Foundation                                                             | 178 |

|   |      | 9.3.4    | Cache coherence modeling for write-through caches                      | 179 |

|   |      | 9.3.5    | Cache coherence modeling for write-back caches                         | 180 |

|   |      | 9.3.6    | Cache coherence modeling in the presence of synchronization constructs | 184 |

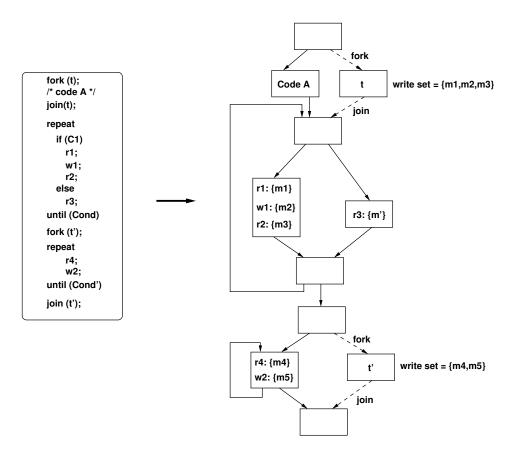

|    | 9.4   | Example                                                       | 185 |

|----|-------|---------------------------------------------------------------|-----|

|    | 9.5   | Chapter summary                                               | 188 |

| 10 | Stati | c Bus Schedule aware Scratchpad Allocation in Multiprocessors | 189 |

| 10 | Stati | e Dus Schedule a ware Scratchpad Anocation in Maniprocessors  | 107 |

|    | 10.1  | Introduction                                                  | 189 |

|    | 10.2  | System and application model                                  | 191 |

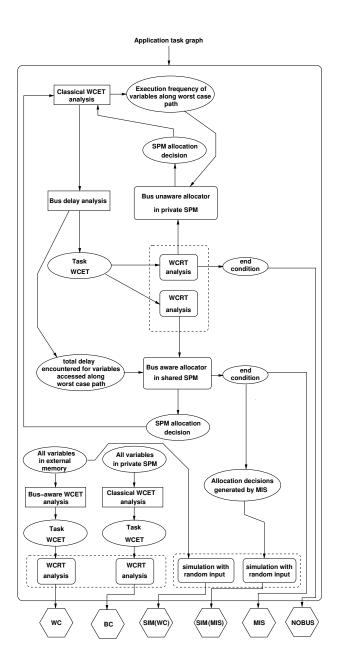

|    | 10.3  | Overview of our SPM allocation framework                      | 192 |

|    | 10.4  | Bus aware WCRT analysis                                       | 196 |

|    | 10.5  | Bus-delay aware Scratchpad allocation                         | 199 |

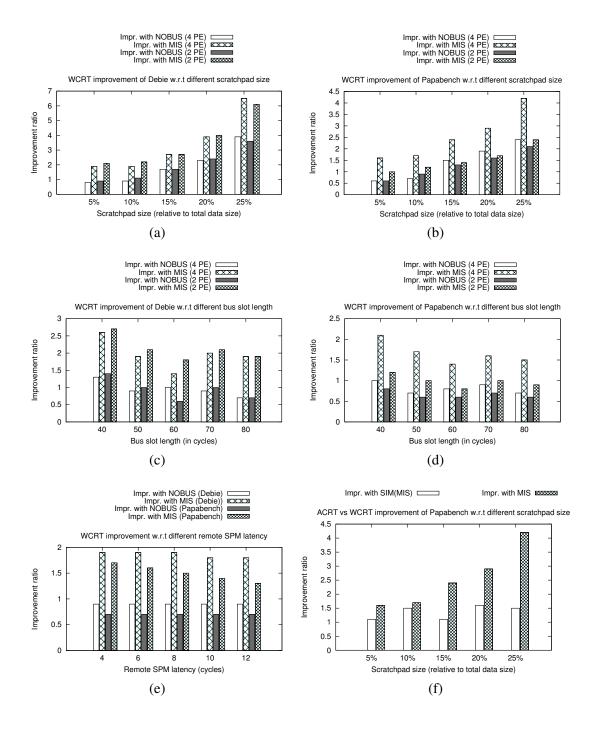

|    | 10.6  | Experimental evaluation                                       | 207 |

|    | 10.7  | Extensions and Future Work                                    | 211 |

|    | 10.8  | Chapter summary                                               | 212 |

|    |       |                                                               |     |

11 Discussion and Future Work

215

## Abstract

Hard real-time systems require absolute guarantees in their execution time. Worst case execution time (WCET) analysis has therefore become a very important problem to address. In recent years, multi-core processors have become widely popular due to their high performance and relatively low power consumption. With the advent of multi-core architectures, WCET prediction has become an increasingly difficult problem. The key to this problem lies in the precise and scalable modeling of shared resources, such as shared cache and shared bus. In this dissertation, we study the modeling of shared cache and shared bus for statically predicting the WCET of an application running on multi-core platform. We show that the timing predictability in multi-core can be achieved both by static analysis and compiler optimization.

We first show that the timing unpredictability due to resource sharing may also appear in single core. A meaningful example of such resource sharing in single core appears in the form of unified cache, which contains both the instruction and data memory blocks. We propose the modeling of two primary shared resources in multi-cores, namely the shared cache and the shared bus, for WCET analysis. We show that the shared cache and the shared bus have nontrivial timing interactions with pipeline and branch prediction. We propose a sound WCET analysis framework which not only models both the shared cache and shared bus, but also models the complex timing interactions of shared cache and shared bus with other basic micro-architectural components (e.g. pipeline, branch predictor). Our experimental results show that we can provide reasonably accurate WCET prediction and we can point the different sources of WCET overestimation. Subsequently, we show the challenges in modeling the shared cache in the presence of preemptive scheduling. We extend our WCET analysis framework with a provably correct shared cache modeling in the presence of preemptive scheduling. Apart from resource sharing, another major source of timing unpredictability in multi-core may appear due to the coherency of shared data items. In this dissertation, we have also presented a WCET analysis framework in the presence of cache coherence.

Finally, we show that the timing unpredictability in multi-core can be reduced by compiler optimization. We have studied the scratchpad allocation problem in multi-processors. We have shown that the presence of shared bus may greatly affect the scratchpad allocation decision and we have proposed a scratchpad allocation algorithm to reduce the bus traffic in multi processor system on chip (MPSoC). Our experimental results have shown that we can significantly reduce the WCET of an application compared to a scratchpad allocation algorithm which ignores shared bus delay.

In summary, this dissertation explores several technical challenges and their possible solutions for hard real-time computing in multi-cores. We believe that the methodologies and frameworks proposed in this dissertation will give valuable insights into the impact of multicore architectures for hard real-time computing.

# **Related Publications**

S. Chattopadhyay and A. Roychoudhury. Unified Cache Modeling for WCET Analysis and Layout Optimizations. In *IEEE Real-time System Symposium* (*RTSS*), 2009.

S. Chattopadhyay, A. Roychoudhury and T. Mitra. Modeling shared Cache and Bus in Multicore Platforms for Timing Analysis. In *International Workshop on Software and Compilers for Embedded Systems* (SCOPES), 2010.

S. Chattopadhyay and A. Roychoudhury. Static Bus Schedule aware Scratchpad Allocation in Multiprocessors. In ACM SIGPLAN/SIGBED Conference on Languages, Compilers, Tools and Theory for Embedded Systems (LCTES), 2011.

S. Chattopadhyay and A. Roychoudhury. Scalable and Precise Refinement of Cache Timing Analysis via Model Checking In *IEEE Real-time System Symposium* (**RTSS**), 2011.

S. Chattopadhyay, L. K. Chong, A. Roychoudhury, T. Kelter, P. Marwedel and H. Falk. A Unified WCET Analysis Framework for Multi-core Platforms In *IEEE Real-time and Embedded Technology and Applications Symposium* (*RTAS*) 2012.

# **List of Tables**

| 4.1  | Example of Persistence Analysis in Unified Cache, $\perp$ represents empty cache line | 30  |

|------|---------------------------------------------------------------------------------------|-----|

| 4.2  | Illustration of data cache analysis, $\perp$ represents empty cache line              | 32  |

| 4.3  | Description of Benchmarks used                                                        | 36  |

| 4.4  | Accuracy and running time of WCET analysis for the different cache configu-           |     |

|      | rations described in Fig. 4.2.                                                        | 36  |

| 4.5  | Reduction in WCET estimates via change in layout                                      | 43  |

| 5.1  | Conflicting task set                                                                  | 57  |

| 5.2  | Standard task set                                                                     | 57  |

| 6.1  | Description of Benchmarks used                                                        | 83  |

| 6.2  | Results from DEBIE (×10 <sup>4</sup> cycles)                                          | 87  |

| 7.1  | Default micro-architectural setting for experiments                                   | 120 |

| 7.2  | Analysis time [of nsichneu] in seconds. The first row represents the analysis         |     |

|      | time when speculative execution was <i>disabled</i> . The second row represents the   |     |

|      | time when speculative execution was <i>enabled</i>                                    | 128 |

| 7.3  | Analysis time [of nsichneu] in seconds. The first row represents the analysis         |     |

|      | time when speculative execution was <i>disabled</i> . The second row represents the   |     |

|      | time when speculative execution was <i>enabled</i>                                    | 128 |

| 8.1  | Papabench task set used in the evaluation                                             | 169 |

| 10.1 | Problem size, analysis time and WCRT                                                  | 210 |

# **List of Figures**

| 1.1 | Interaction of schedulability analysis and WCET analysis                              | 3  |

|-----|---------------------------------------------------------------------------------------|----|

| 1.2 | (a) A program control flow graph with two paths, (b) layout of the program code       |    |

|     | in memory, showing the instruction cache misses                                       | 3  |

| 1.3 | (a) A simple program with $2^{100}$ program paths, array a is an input, (b) a single- |    |

|     | path program fragment where WCET cannot be obtained by executing one path             | 5  |

| 2.1 | An example program and its corresponding control flow graph (CFG)                     | 9  |

| 2.2 | An example showing timing anomaly. (a) Execution scenario with $I1$ facing            |    |

|     | instruction cache hit, (b) execution scenario with $I1$ facing instruction cache miss | 11 |

| 2.3 | Overview of a typical WCET analysis framework                                         | 12 |

| 2.4 | An example showing ILP-based WCET calculation                                         | 13 |

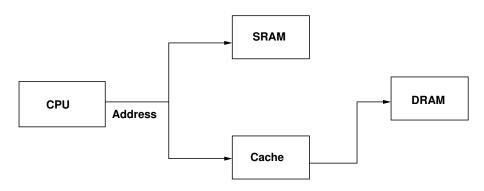

| 3.1 | Addressing mechanism in the scratchpad memory and the cache                           | 23 |

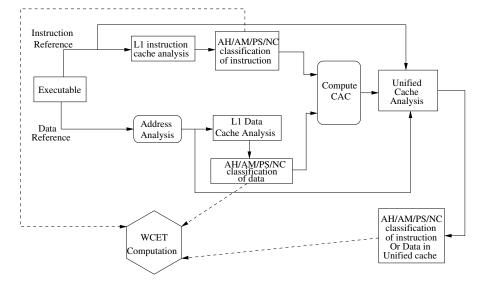

| 4.1 | Overview of Cache Modeling Framework                                                  | 28 |

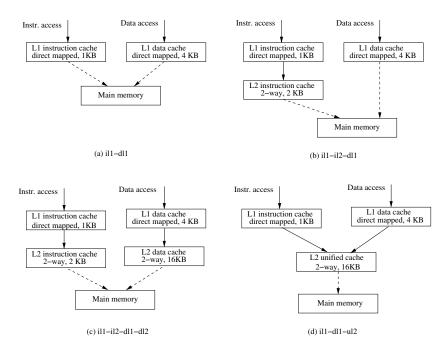

| 4.2 | Different cache configurations used in experiments                                    | 35 |

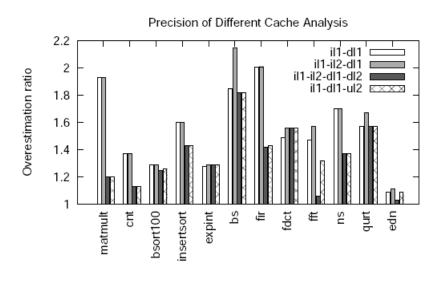

| 4.3 | WCET overestimation for the cache configurations in Fig. 4.2                          | 37 |

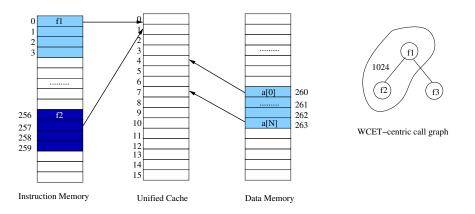

| 4.4 | Code and data layout before procedure positioning                                     | 39 |

| 4.5 | Code and data layout after procedure positioning by [1]                               | 39 |

| 4.6 | WCET-centric unified graph                                                            | 41 |

| 4.7 | Transforming the unified graph of Figure 4.6                                          | 42 |

| 4.8 | Final layout after our code + data positioning                                        | 42 |

| 5.1 | (a) inter-core cache conflicts, (b) General framework of our WCET analysis            |    |

|     | which combines abstract interpretation and model checking                             | 49 |

| 5.2 | Example program and its corresponding control flow graph (CFG) without the            |    |

|     | backedge                                                                              | 51 |

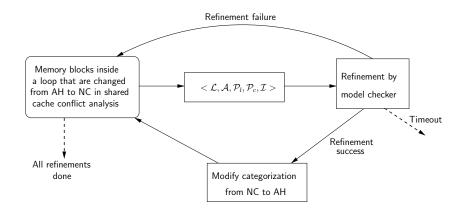

| 5.3  | Refinement of shared cache conflict analysis                                                          | 52  |

|------|-------------------------------------------------------------------------------------------------------|-----|

| 5.4  | Inter-core cache conflict refinement                                                                  | 52  |

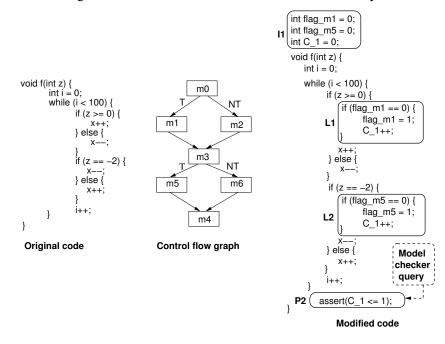

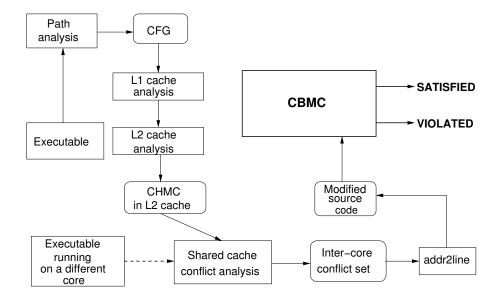

| 5.5  | Implementation framework using CBMC                                                                   | 56  |

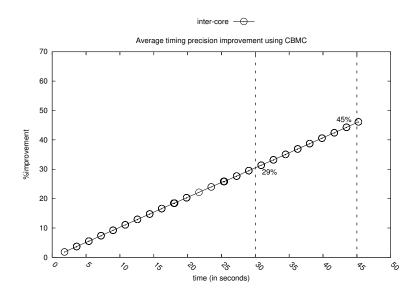

| 5.6  | Timing precision improvement w.r.t. time using <i>statemate</i> and CBMC                              | 58  |

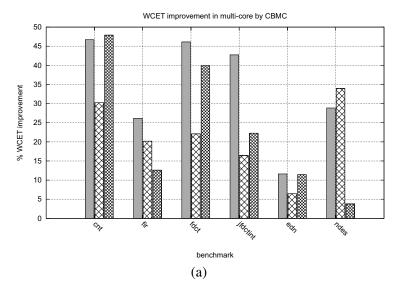

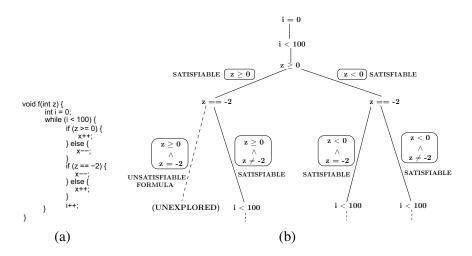

| 5.7  | (a) WCET improvement in multi-core using CBMC, (b) analysis time using                                |     |

|      | СВМС                                                                                                  | 59  |

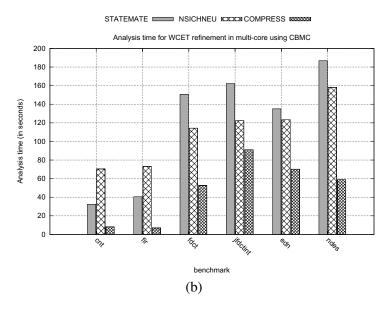

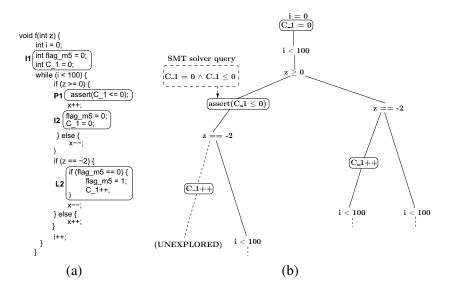

| 5.8  | (a) Example program, (b) KLEE symbolic execution                                                      | 61  |

| 5.9  | (a) Transformed code for checking cache conflict, (b) checking the assertion                          |     |

|      | during KLEE symbolic execution                                                                        | 62  |

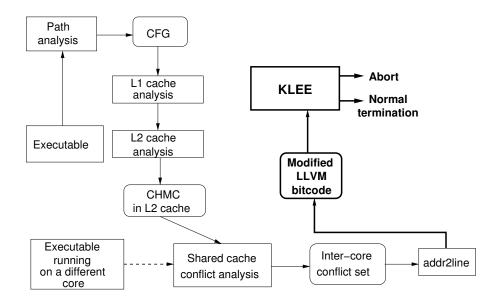

| 5.10 | Implementation framework using KLEE                                                                   | 64  |

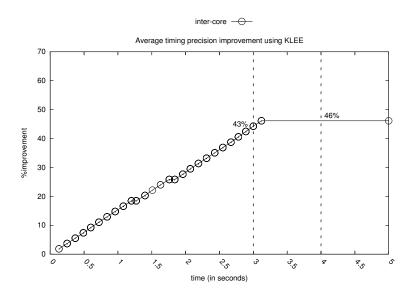

| 5.11 | Timing precision improvement w.r.t. time using statemate and KLEE                                     | 65  |

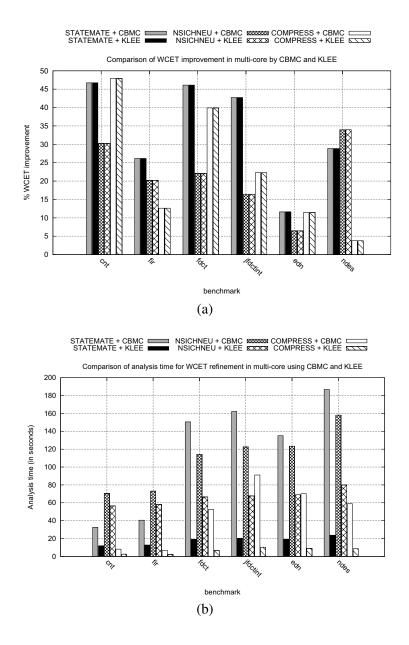

| 5.12 | (a) Comparison of multi core WCET improvement using CBMC and KLEE, (b)                                |     |

|      | comparison of analysis time using CBMC and KLEE                                                       | 66  |

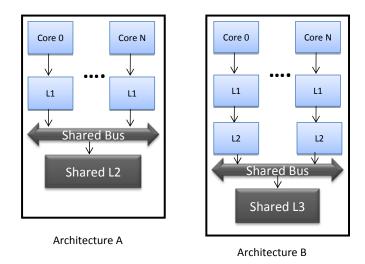

| 6.1  | Multi-core cache memory hierarchy.                                                                    | 70  |

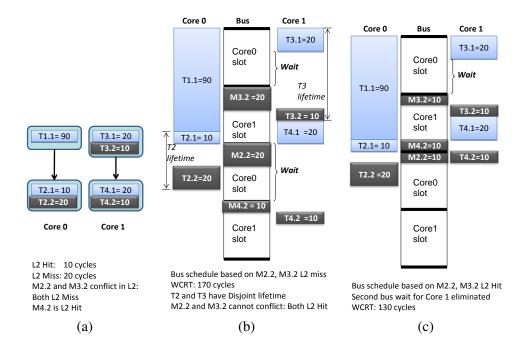

| 6.2  | Example to show dependency between cache and bus analysis                                             | 71  |

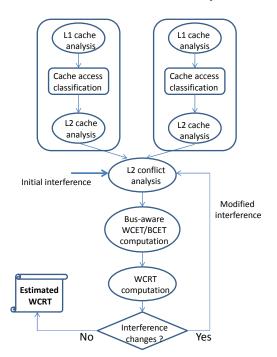

| 6.3  | Our analysis framework                                                                                | 72  |

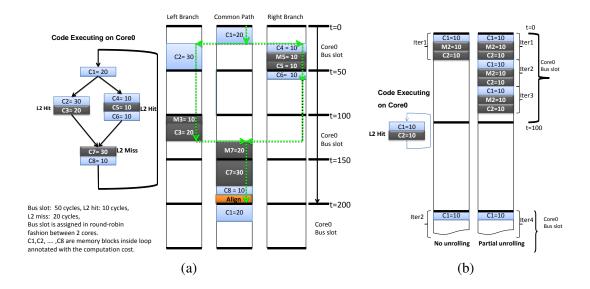

| 6.4  | (a) An example of loop analysis (b) Limited loop unrolling for loop iterations                        |     |

|      | with low cost.                                                                                        | 75  |

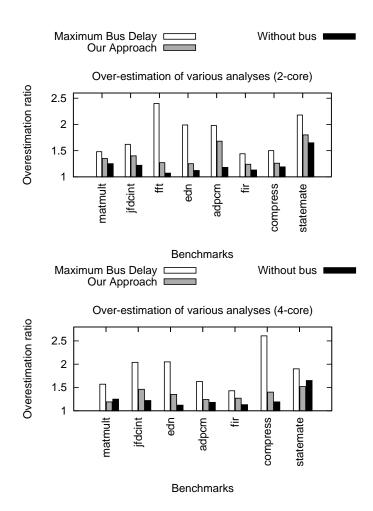

| 6.5  | Overestimation in WCET analysis                                                                       | 84  |

| 6.6  | Sensitivity of WCET analysis with bus slot length                                                     | 85  |

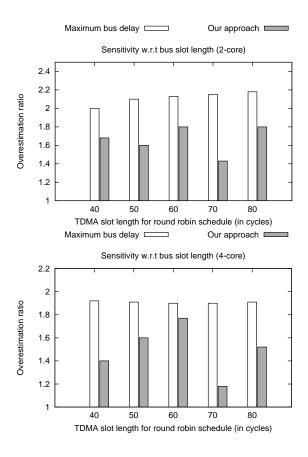

| 6.7  | DEBIE task graph and task sizes                                                                       | 86  |

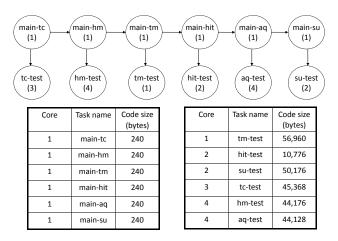

| 6.8  | A multi-processor architecture featuring on-chip shared L2 cache                                      | 88  |

| 7.1  | Execution graph for the example program in a 2-way superscalar processor with                         |     |

|      | 2-entry instruction fetch queue and 4-entry reorder buffer. Solid edges show                          |     |

|      | the dependency between pipeline stages, whereas the dotted edges show the                             |     |

|      | contention relation                                                                                   | 92  |

| 7.2  | Overview of our analysis framework                                                                    | 94  |

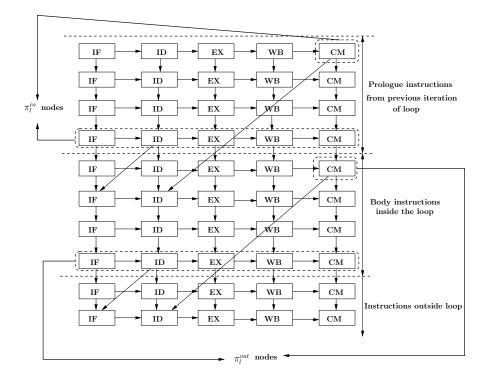

| 7.3  | $\pi_l^{in}$ and $\pi_l^{out}$ nodes shown with the example of a sample execution graph. $\pi_l^{in}$ |     |

|      | nodes propagate bus contexts across iterations, whereas, $\pi_l^{out}$ nodes propagate                |     |

|      | bus contexts outside of loop.                                                                         | 100 |

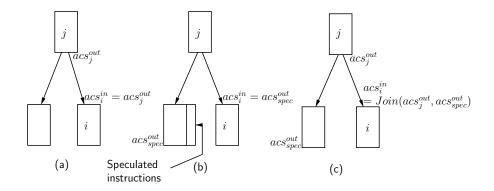

| 7.4 (a) Computation of $acs_i^{in}$ when the edge $j \rightarrow i$ is correctly predicted, (b) Com-      |     |

|-----------------------------------------------------------------------------------------------------------|-----|

| putation of $acs_i^{in}$ when the edge $j \rightarrow i$ is mispredicted, (c) A <i>safe</i> approximation |     |

| of $acs_i^{in}$ by considering both correct and incorrect prediction of edge $j \rightarrow i$ 1          | 06  |

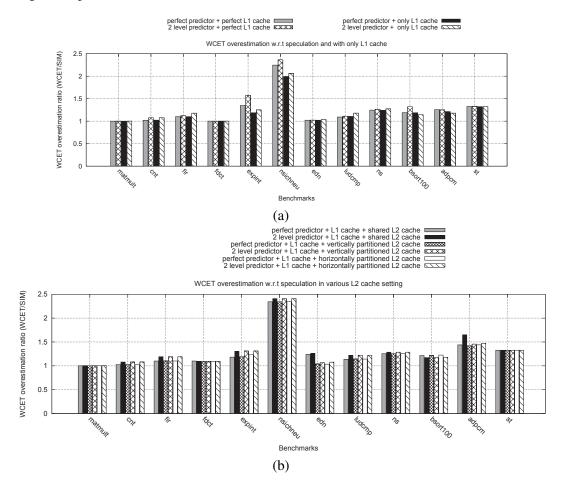

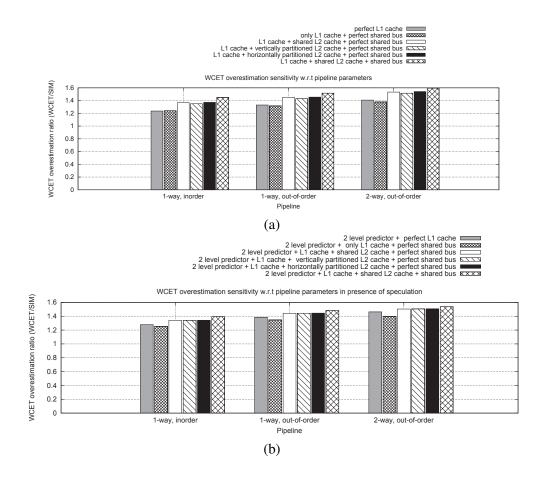

| 7.5 Effect of shared and partitioned L2 cache on WCET overestimation 1                                    | 21  |

| 7.6 (a) Effect of speculation on L1 cache, (b) effect of speculation on partitioned                       |     |

| and shared L2 caches                                                                                      | 22  |

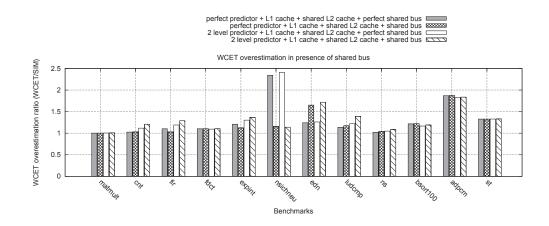

| 7.7 Effect of shared bus on WCET overestimation                                                           | 23  |

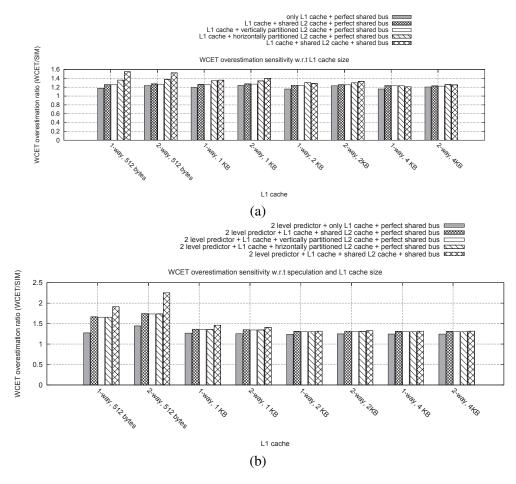

| 7.8 WCET overestimation sensitivity w.r.t. L1 cache (a) without speculation, (b)                          |     |

| with speculation                                                                                          | 24  |

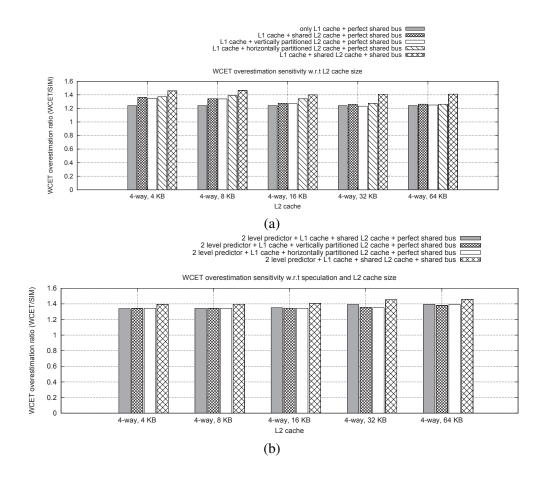

| 7.9 WCET overestimation sensitivity w.r.t. L2 cache (a) without speculation, (b)                          |     |

| with speculation                                                                                          | 25  |

| 7.10 WCET overestimation sensitivity w.r.t. different pipelines (a) without specula-                      |     |

| tion, (b) with speculation                                                                                | .26 |

| 7.11 WCET overestimation sensitivity w.r.t. different bus slot length (with and with-                     |     |

| out speculative execution)                                                                                | .27 |

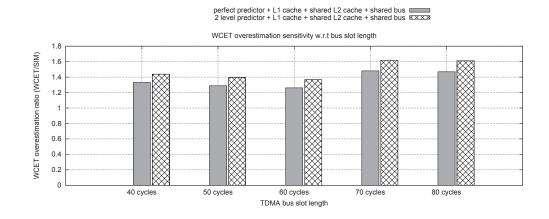

| 7.12 Analysis of cache in the presence of FIFO replacement policy (a) WCET over-                          |     |

| estimation w.r.t. different L2 cache architectures, (b) WCET overestimation in                            |     |

| the presence of FIFO cache and speculative execution                                                      | 32  |

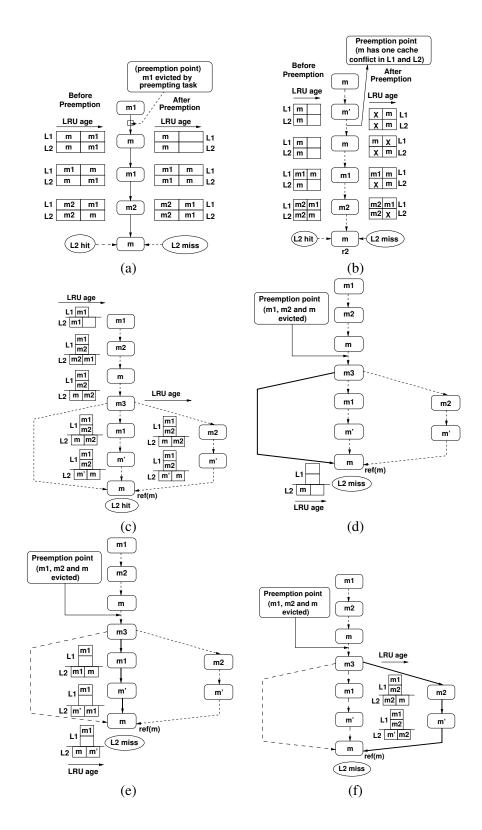

| 8.1 CRPD analysis framework                                                                               | 36  |

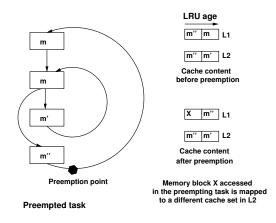

| 8.2 Cache reload delay due to the <i>indirect effect of preemption</i>                                    | 38  |

| 8.3 For all the figures, LRU age direction has been indicated. The direction of                           |     |

| the arrow labelled "LRU age" points to the older age blocks. (a): Due to the                              |     |

| indirect effect of preemption, preemption cost must go through all the memory                             |     |

| references (not just all the memory blocks). The phenomenon is shown for                                  |     |

| memory block $m$ . (b): In the figure, an L2 cache miss occurs for the second                             |     |

| access (but first access to L2 cache) of $m$ after preemption. (c)&(d)&(e)&(f):                           |     |

| Demonstrating the indirect effect of preemption. (c): L1 and L2 cache contents                            |     |

| in the absence of preemption, (d)&(e)&(f): The solid paths are the executed                               |     |

| paths (in the order (d) $\rightarrow$ (e) $\rightarrow$ (f)) after preemption. L1 and L2 cache contents   |     |

| after preemption are shown when the solid path is executed                                                | 39  |

| 8.4 CRPD analysis framework in the presence of shared caches                                              | 51  |

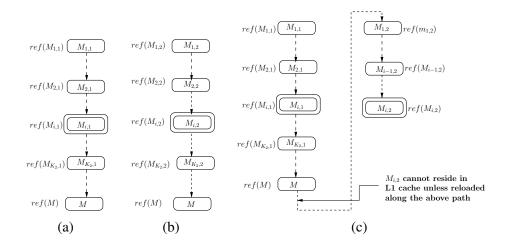

| 8.5  | Bounding the indirect effect of preemption when $S_1 \leq S_2$ and $K_1 \leq K_2$ .   |      |

|------|---------------------------------------------------------------------------------------|------|

|      | $ref(M_{i,1})$ and $ref(M_{i,2})$ are L1 cache hits in the absence of preemption, but |      |

|      | access the L2 cache after preemption. (a)&(b): Indirect preemption effect cre-        |      |

|      | ated on $ref(M)$ , (c): a scenario which shows that (a)&(b) cannot happen togethe     | r160 |

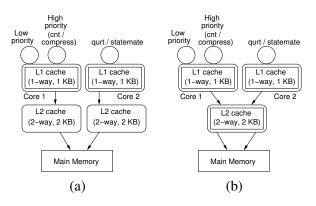

| 8.6  | We use either cnt or compress [2] to generate inter-task cache conflict. (a)          |      |

|      | Default architecture used for the results reported as "preemption + no L2 cache       |      |

|      | sharing". (b) Default architecture used for the results using shared cache. Either    |      |

|      | qurt or statemate [2] is used to generate inter-core cache conflicts                  | 166  |

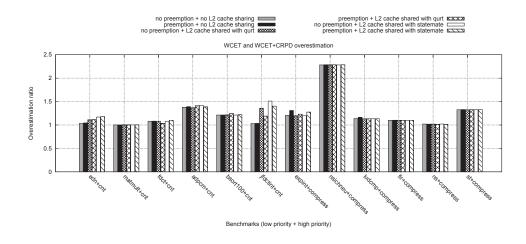

| 8.7  | WCET + #p.CRPD overestimation for the task set used from [2]. A combina-              |      |

|      | tion of $A + B$ along the x-axis denotes the scenario when task A is preempted        |      |

|      | by task $B$ (where applicable)                                                        | 167  |

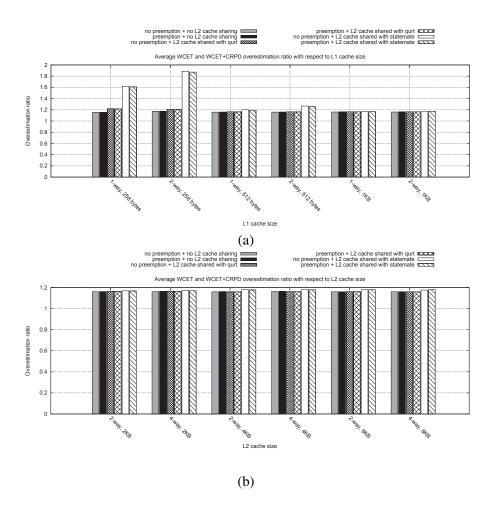

| 8.8  | CRPD and WCET analysis sensitivity with respect to (a) L1 cache configuration         |      |

|      | and (b) L2 cache configuration                                                        | 168  |

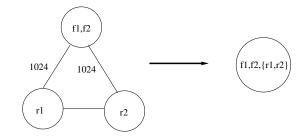

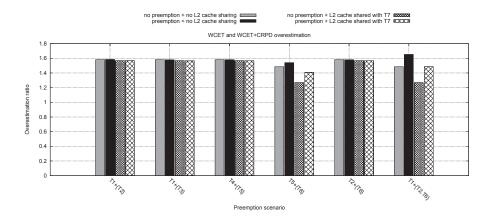

| 8.9  | WCET + #p.CRPD overestimation for the task set used from papabench.                   |      |

|      | A combination of $A + \{B\}$ along the x-axis denotes the scenario when task A        |      |

|      | is preempted by the set of tasks in $B$ (where applicable)                            | 170  |

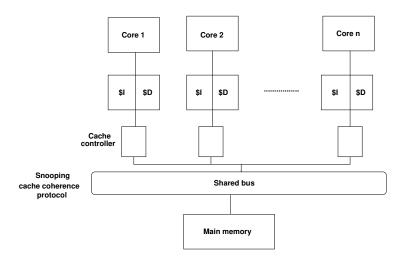

| 9.1  | Multi-core architecture used for coherence miss modeling                              | 173  |

| 9.2  | Overview of our analysis framework                                                    | 175  |

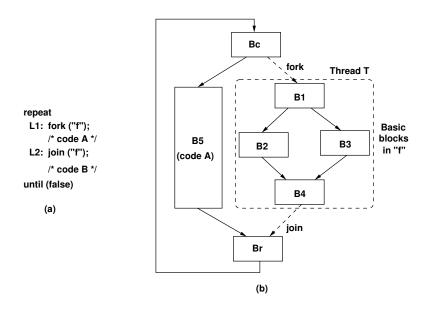

| 9.3  | fork and join construct in a parallel program                                         | 177  |

| 9.4  | Example program and the respective control flow graph with fork-join con-             |      |

|      | structs                                                                               | 186  |

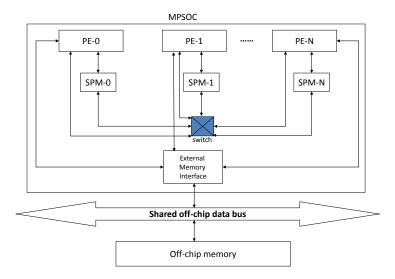

| 10.1 | System Architecture                                                                   | 191  |

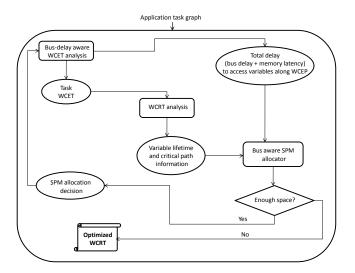

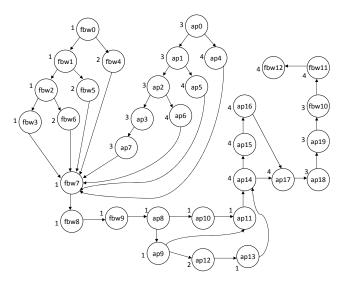

| 10.2 | Overview of SPM allocation framework                                                  | 192  |

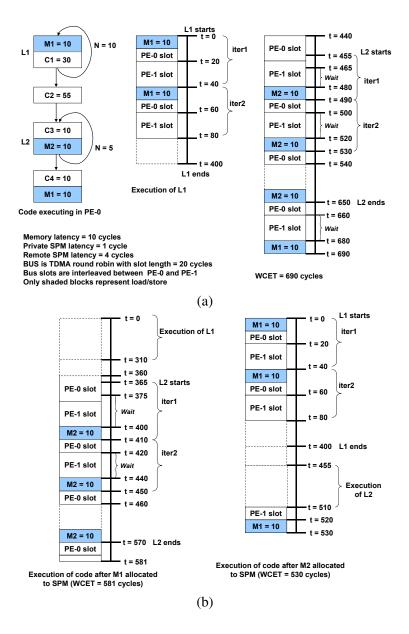

| 10.3 | (a) A sample code and its execution without SPM allocation (b) Execution of           |      |

|      | the code by two possible SPM allocations                                              | 193  |

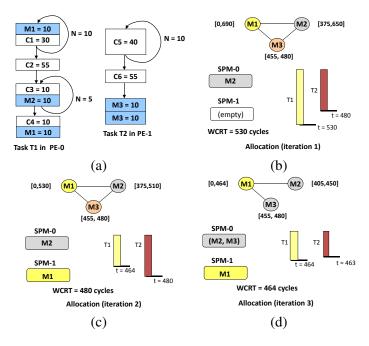

| 10.4 | Iterative SPM allocation scheme shown on two tasks T1, T2 running on different        |      |

|      | processors. Task T1 is same as the example in Fig. 10.3                               | 195  |

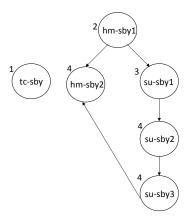

| 10.5 | Task graph extracted from DEBIE-DPU                                                   | 208  |

| 10.6 | Task graph of <i>papabench</i>                                                        | 208  |

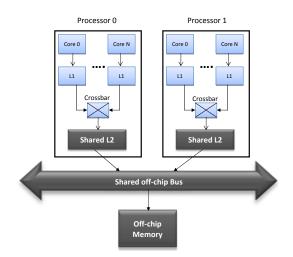

| 10.7 | Experimental setup                                                                    | 209  |

|      |                                                                                       |      |

### Chapter 1

## Introduction

Many of our daily life functionalities are controlled by embedded systems, such as MP3 players, washing machines, automobiles and so on. An embedded system runs a specific application for its entire lifetime. Therefore, the validation of an embedded system requires the validation of the specific application running on the system. In a way, therefore, validating an embedded system is apparently easier than validating a general purpose system, as the validation engineer has to focus upon exactly one application. On the other hand, most of the embedded software are required to satisfy some extra-functional properties, such as timing. Such time-constrained systems are not only expected to generate a *correct* output, but they are also expected to generate the correct output within *specified time bound*. These systems are also widely known as *real-time embedded systems*.

#### **1.1 Real-time embedded systems**

Real-time embedded systems can broadly be classified into two categories: *hard real-time systems* and *soft real-time systems*. Hard real-time systems need critical timing guarantees. Violation of such timing constraints for hard real-time systems may generate catastrophic effects. A typical example of a hard real-time system could be an *anti-lock braking system* (ABS) from automotive domain. An ABS is a safety system which allows the wheels of a vehicle to interact with the ground while braking and thereby avoids the vehicle to slide on the ground surface. Note that the response time of an ABS system is crucial and it needs hard real-time guarantees. The violation of such hard real-time guarantee may lead to serious consequences, such as a car accident. Soft real-time systems, on the other hand, can tolerate a certain number of violation in timing constraints. A typical example of a soft real-time system could be a video streaming device. In video streaming, a certain amount of delay could be tolerable. As long as the interarrival time between two video frames does not disturb the human viewing perception, we can say that the quality of the respective video streaming device is acceptable.

#### 1.1.1 Analysis of hard real-time systems

Since the timing constraints are critical for hard real-time systems, the timing behavior of such systems must be known at the design time. As an example, for the ABS safety system, we must know the upper bound on the brake controller's response time. In this way, the driver of the vehicle can determine a suitable position for braking and she can avoid any serious accident. The upper bound on the application response time is widely known in literature as *worst case response time* (WCRT). The analysis of worst case response time can be classified into two different levels as follows:

**Worst case execution time analysis** Worst case execution time (WCET) of a program gives an upper bound on the execution time of the program for all possible inputs [3]. Knowing worst case execution time is of prime importance for the WCRT analysis. Since exhaustive enumeration of all possible inputs is often infeasible, WCET is in general determined through a static program analysis. WCET analysis considers the execution time of an isolated task and the tasks are assumed never to block or to be interrupted. Blocking or interruption is taken care by the WCRT analysis. Clearly, WCET of a task depends on the underlying hardware platform and its corresponding micro-architectural parameters (e.g., size of cache, pipeline). Therefore, WCET analysis, in general estimates the execution time of a task for a given hardware platform.

**System level or schedulability analysis** In schedulability analysis, overall system performance is analyzed given the results of WCET analysis for each task. The scheduling could be preemptive or non-preemptive. Each task is assigned a deadline and an application is schedulable if all tasks in the application can meet their deadline. The correctness and precision of schedulability analysis thus very much depends on the accuracy and precision of WCET analysis. If WCET values are underestimated (i.e., less than the actual worst case execution time), schedulability analysis may predict an application to be schedulable even though some task may not meet its deadline in actual execution. This kind of error is considered catastrophic in hard

real-time systems and it may lead to serious consequences. On the other hand, if WCET values are pessimistic (much greater than the actual worst case execution time of task) then the scheduler will be forced to allocate more time to those tasks than actually required and thereby leading to a very imprecise schedulability analysis.

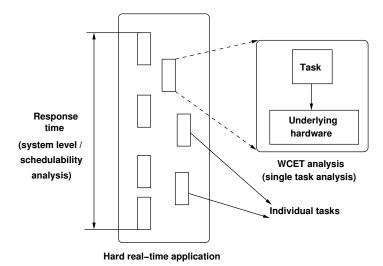

Figure 1.1: Interaction of schedulability analysis and WCET analysis

Figure 1.1 shows the dependency of schedulability analysis on WCET analysis. A real-time application typically contains multiple tasks. As shown in Figure 1.1, schedulability analysis computes the response time of the overall application. This analysis takes the WCET of each component task as input and it is usually oblivious to the low-level micro-architectural details (*e.g.* pipeline, cache). On the other hand, WCET analysis of each task is highly sensitive to the underlying micro-architecture and computes the WCET of a single task for a given hardware platform, as also shown in Figure 1.1.

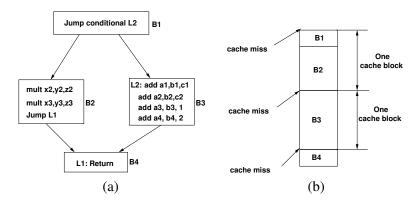

Figure 1.2: (a) A program control flow graph with two paths, (b) layout of the program code in memory, showing the instruction cache misses

The underlying hardware platform has a serious impact on the WCET of an application. Through a simple example in Figure 1.2, we shall show why the timing effects of the underlying micro-architecture cannot be ignored for a sound WCET analysis. Figure 1.2(a) shows the control flow graph (CFG) of a program fragment. The program fragment has exactly two paths: i) B1-B2-B4 and ii) B1-B3-B4. Basic block B2 has a set of multiplication (mult) instructions and basic block B3 has a set of addition instructions (add). Since multiplication is much more expensive than addition, without considering any micro-architectural effects, we can conclude that B1-B2-B4 is the worst case execution path. Now consider the presence of an instruction cache and assume that the example program fragment has been loaded in memory as shown in Figure 1.2(b). If a cache block can hold four instructions, basic block B2 will not suffer any cache miss. However, basic block B3 will suffer a cache miss to load the first instruction in B3. As a result, the execution path B1-B2-B4 will suffer two cache misses (one each at the beginning of basic block B1 and basic block B4), whereas, the execution path B1-B3-B4 will suffer three cache misses (one each at the beginning of each basic block). Since cache miss penalty is a magnitude higher than the processor clock cycle, B1-B3-B4 might become the worst case execution path. Therefore, we conclude that the timing effects of the underlying hardware platform is of prime importance for a sound WCET estimate.

#### 1.1.2 Can we use software testing to find WCET?

In general, it is infeasible to find the WCET of a task through *software testing*. Finding WCET through software testing involves executing the respective application for different inputs and recording the maximum execution time. However, it is usually expensive to enumerate all possible inputs of an application. Moreover, testing all permutations of inputs require clear domain knowledge of the application. Consider a simple program which sorts 10 given integers. Assuming a 32 bit integer, there are  $2^{32*(10)}$  different permutations of inputs to the sorting program and testing the sorting program for all  $2^{32*(10)}$  inputs is clearly infeasible. Similarly, consider a video processing application, such as an MPEG encoder. Finding the WCET of an MPEG encoder through software testing involves executing the MPEG encoder for a potentially unbounded number of videos. Therefore, even with sufficient knowledge of an application, it is usually infeasible to test the application for all possible inputs.

It might appear to the reader that testing all different permutations of different inputs is not necessary for finding WCET. The reader might think that it might be possible to find the WCET

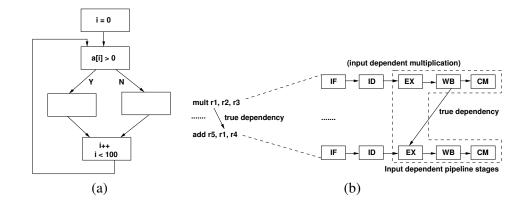

Figure 1.3: (a) A simple program with  $2^{100}$  program paths, array a is an input, (b) a single-path program fragment where WCET cannot be obtained by executing one path

by testing all possible execution paths of a program. Such a phenomenon is commonly known as obtaining *path coverage*. For the time being, assume that WCET can be computed by obtaining path coverage. However, obtaining path coverage is also expensive, as shown by the program in Figure 1.3(a). If the array "a" is an input, the program has  $2^{100}$  possible execution paths. As a result, obtaining path coverage is infeasible in practice and so as finding WCET through software testing.

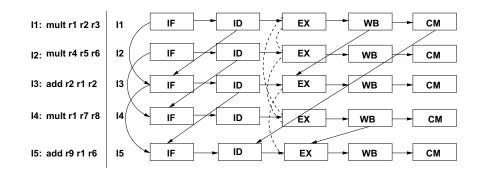

Finally, we show that covering all the paths of a program may not necessarily expose the WCET of the program. Assume that we want to compute the WCET of a straight line program fragment shown in Figure 1.3(b). The program is shown at the assembly code level to demonstrate the technical issue. Figure 1.3(b) also shows the execution of the program fragment in a conventional five stage pipeline (*i.e.* IF-ID-EX-WB-CM). The result produced by the multiplication instruction (e.g. mult) is used by the addition (e.g. add). This dependency is shown by the solid edge between the WB and the EX pipeline stages of the two instructions. In general, a multiplication instruction has variable latencies (which depends on the operands). Therefore, if the multiplication instruction is *input dependent*, the EX stage of the addition instruction will finish at different time points (depending on the concrete input values), which in turn will affect the WCET of the program fragment. Such input dependent pipeline stages are highlighted in Figure 1.3(b). However, note that it was sufficient to obtain program path coverage of the program fragment by generating just *one* concrete input. In general, for a single program path, there are different execution scenarios at the micro-architectural level. One such example is shown in Figure 1.3(b). However, in the presence of advanced micro-architectural features (e.g. superscalar and out-of-order pipeline, speculative execution) the situation is far more complex and a single program path may lead to a huge number of execution scenarios depending on the concrete values of inputs.

Therefore, we conclude that conventional software testing *may miss* the program input for which the actual worst case execution time of the program is reached. Consequently, a *sound* WCET (*i.e.* a true upper bound on the execution time over all possible inputs) of a program cannot be obtained solely by software testing. On the other hand, a conservative static program analysis technique can analyze the program irrespective of the program's input. Consequently, it is possible to obtain a *sound* upper bound of the actual WCET of a program through static program analysis.

#### **1.2** Motivation and thesis overview

As we describe in the preceding, WCET analysis of a program depends on the underlying hardware platform. With the advent of multi-core architectures, multi-core processors have been adopted for mainstream computing due to the high performance and low power consumption offered by such processors. Therefore, it is reasonable to adopt the advantages of multi-core processors in the area of real-time embedded systems. Whereas multi-core processors offer several performance and power related advantages, they pose significant challenges to be adopted for hard real-time systems. Multi-core processors extensively employ shared resources (e.g. shared cache, shared bus). The presence of shared resources drastically increases the timing unpredictability, as the timing largely depends on the nature of conflicts generated in the shared resources. The conflicts in the shared resource, on the other hand, highly depend on the applications running on different cores. To adopt multi-core processors for hard real-time systems, it is necessary to predict the execution time of an application. In this dissertation, we have performed an in-depth study of WCET analysis of programs running on multi-core platforms. Our modeling of shared cache and shared bus can be used for statically predicting the WCET of an application running on multi-core platforms. Moreover, our WCET analysis framework can be used to pinpoint the sources of WCET overestimation and it can be used for specialized compiler optimizations to achieve time predictability. As evidenced by our scratchpad allocation optimization, such an analysis framework can help to reduce the timing unpredictability arising due to a shared bus in multi-core.

#### **1.3** Organization of the chapters

In this dissertation, we concentrate on static WCET analysis in the presence of multi-core architectures. Multi-core architectures extensively employ shared resources (e.g., shared cache, shared bus etc) and introduction of shared resources makes WCET analysis a very challenging problem due to the unpredictable conflicts generated in the same. Among others, shared cache and shared bus are two meaningful examples of resource sharing in multi-cores (where the conflicts are generated at the level of memory references from different tasks running on different processor cores). Resource sharing can also be found in single-core architectures. Unified cache, where the conflicts are generated at the level of instruction and data memory blocks, is a key example for resource sharing in single-core architecture. We therefore introduce our work by modeling the unified cache for WCET analysis in Chapter 4 and later move on to model the shared cache and the shared bus in multi-cores in Chapter 5 and Chapter 6, respectively. In Chapter 7, we propose a unified WCET analysis framework which models the complex timing interactions between the shared resources and other basic micro-architectural components (e.g. pipeline, branch predictor). In Chapter 8, we extend our framework in the presence of preemptive multi-tasking systems. In Chapter 9, we show that the timing unpredictability in multi-core system may also appear due to the coherency of data items shared by multiple cores. We also present a WCET analysis framework in the presence of cache coherence in Chapter 9. Finally, in Chapter 10, we shall describe how our analysis framework can be used to reduce the conflicts in shared resources through a compiler optimization pass. More specifically, we show that the shared bus traffic can be reduced by selecting appropriate contents in software controlled scratchpad memories. In Chapter 11, we shall conclude this dissertation and discuss possible future directions.

### Chapter 2

## WCET Analysis Background

In this Chapter, we shall introduce a general background on *worst case execution time* (WCET) analysis. We shall discuss the different phases required for static prediction of WCET, as well as the related technical issues associated with each of these phases.

#### **2.1** Static WCET analysis

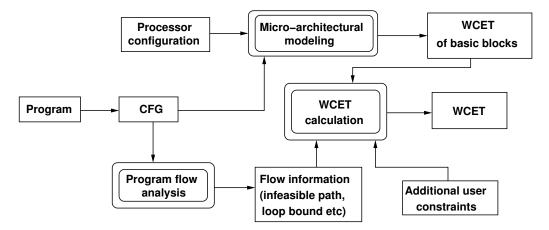

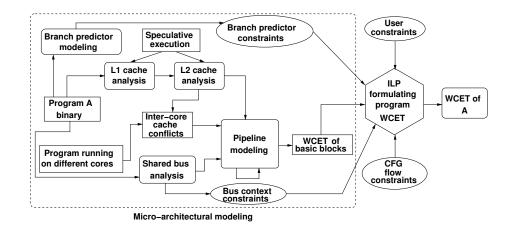

Static WCET estimation typically involves three phases: program flow analysis (to find the infeasible program path and loop bound), micro-architectural modeling (to find the timing effects of underlying hardware) and a calculation phase to find the longest feasible program path using the results of program flow analysis and micro-architectural modeling. In the following, we shall briefly discuss each of these three analysis phases.

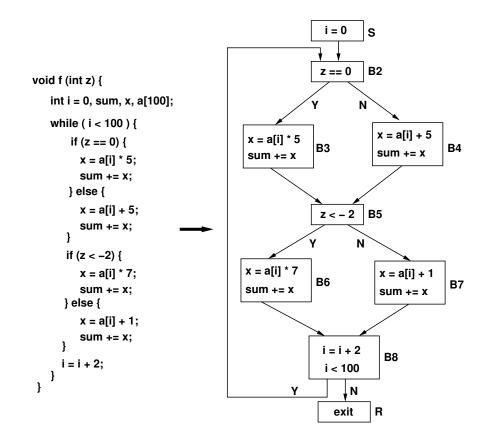

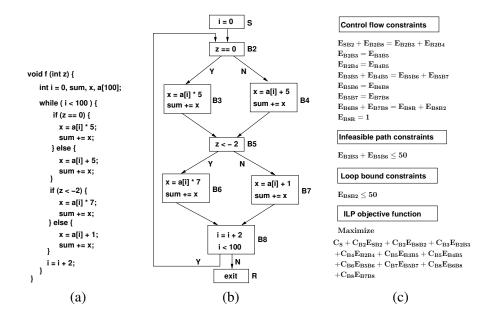

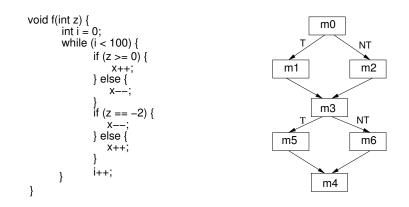

**Program flow analysis** The goal of program flow analysis is to find infeasible program paths and loop bounds. The *soundness* of WCET analysis is not affected by infeasible program paths. However, with the knowledge of infeasible paths, the static WCET analyzer can ignore certain paths during WCET computation. This in turn may lead to a tighter WCET estimation. Consider an example program and its corresponding control flow graph (CFG) shown in Figure 2.1. Without any knowledge of infeasible path, assume that the WCET analyzer computes B2-B3-B5-B6-B8 as the worst case path inside the loop. However, careful examination reveals that the condition of basic block B2 (*i.e.* z == 0) and basic block B5 (*i.e.* z < -2) cannot be satisfied together for any execution. Therefore, B2-B3-B5-B6-B8 captures an *infeasible execution* and therefore, it can be ignored during the WCET analysis. In general, if such infeasible path information can be integrated into a WCET analyzer, the analysis may lead to a more

Figure 2.1: An example program and its corresponding control flow graph (CFG)

precise WCET estimate by focusing on a lesser number of possible execution paths.

Whereas the discovery of infeasible paths may only affect the precision of WCET analysis, WCET prediction is not possible without knowing the upper bound of all loop iterations in the program. In the example shown in Figure 2.1, it is not possible to predict the WCET of function f without knowing that the loop iterates 50 times. Therefore, discovering the upper bound on loop iteration is potentially more important for an accurate WCET prediction.

The research on flow analysis has focused on automatic discovery of infeasible paths as well as loop bounds [4; 5; 6; 7]. If the upper bound on loop iteration cannot be inferred statically, such an upper bound can be provided manually to the WCET analyzer in the form of user annotations. Similarly, certain infeasible program paths might be provided manually to the WCET analysis tool to get a tighter WCET estimation.

**Micro-architectural modeling** WCET of an application is highly sensitive to the underlying hardware platform. Therefore, to predict a *sound* and *precise* WCET of an application, the timing effects of the underlying hardware need to be modeled. Micro-architectural modeling analyzes the timing effects of underlying hardware components (*e.g.* pipeline, cache, branch

predictor etc) and it is the crucial part of WCET analysis process. In past two decades, an extensive amount of research effort has been put forward for micro-architectural modeling. One of the first few approaches include the use of integer linear programming (ILP) [8], but the use of ILP poses scalability issues due to the presence of a huge number of ILP constraints. However, the breakthrough in micro-architectural modeling was first proposed in [9]. The work in [9] has proposed a scalable approach of using abstract interpretation for micro-architectural modeling. Since its inception [10], abstract interpretation has been successfully applied to many application domain including functionality testing and compiler optimization. In [9], abstract interpretation was proposed to be used for WCET analysis. The basic framework proposed in [9] has later been extended by many research efforts to analyze advanced micro-architectural features, such as data cache [11], multi-level cache [12], pipeline [13], branch predictor [14], shared cache [15] and so on.

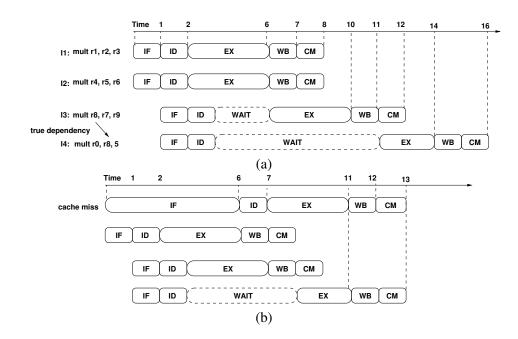

Micro-architectural modeling for modern processors is complicated due to a commonly known phenomenon called *timing anomaly* [16]. Assume a sequence of instructions containing a particular instruction I. Further assume that I have two possible latencies  $L_1$  and  $L_2$ , which lead to a total execution time of  $E_1$  and  $E_2$ , respectively, for the sequence of instructions. Note that I might have variable latencies due to different reasons, such as, *cache hit/miss*, variable execution cycle (*e.g.* multiplication instruction) and so on. A *timing anomaly* occurs when  $L_1 < L_2$ , but  $E_1 > E_2$ . Timing anomaly is best explained by an example. We shall use the example shown in Figure 2.2 to illustrate the problem.

Figure 2.2(a) shows a sequence of multiplication instructions and its execution in a multipleway, superscalar processor. The fourth instruction has a dependency on the third instruction due to the computation in register r8. Additionally, for the sake of illustration, we assume the following:

- Multiplication has variable execution latency 1 ~ 4 cycles. First three multiplication instructions take 4 cycles to execute and the fourth instruction takes 3 cycles to execute.

- Cache miss penalty is 6 cycles.

- There are a total of two multiplier units.

We shall consider two execution scenarios:  $(EX_1)$  the first instruction is an *instruction cache* hit, and  $(EX_2)$  the first instruction is an *instruction cache miss*.

Figure 2.2: An example showing timing anomaly. (a) Execution scenario with I1 facing instruction cache hit, (b) execution scenario with I1 facing instruction cache miss

In  $EX_1$  (shown in Figure 2.2(a)), instruction I3 has to wait till 6th cycle as the two multiplier units are occupied by I1 and I2. Since I4 depends on the result computed by I3, I4 also has to wait for I3 to finish execution. Eventually, the sequence of instructions I1, I2, I3, I4 finishes in 16 cycles.

Now consider the second execution scenario where I1 is an instruction cache miss (shown in Figure 2.2(b)). In this case, I3 can finish execution at 7th cycle using one of the free multiplier units. Subsequently, I4 can finish execution at 11th cycle and the sequence of instructions finishes in 13 cycles.

From the above example, we observe that a *cache hit* (which is a local worst case scenario) leads to an overall *worse* execution time compared to a *cache miss*. Such counter intuitive phenomenon appears due to the complex timing interactions between cache and pipeline. The example in Figure 2.2 also demonstrates that it is insufficient to track the local worst case of each instruction (such as a cache miss rather than a cache hit) to compute the WCET of an entire program. As a result, to compute the WCET of a program, one needs to keep track of the different micro-architectural states and their possible permutations. However, capturing all possible micro-architectural states via abstract interpretation [9; 13] or timing interval abstraction to capture the time taken by each pipeline stage [17; 18].

**Path analysis** Path analysis uses the results by program flow analysis and micro-architectural modeling to find the longest feasible program path in the program. Among others, *path-based technique* and *implicit path enumeration* are mostly used for the calculation of WCET.

*Path-based techniques* try to find the WCET of the program by enumerating feasible program paths and then searching for the program path having longest execution time. Path-based techniques are naturally very precise and these techniques can also integrate various program flow information (computed during flow analysis) while searching for the longest path. Pathbased WCET calculation has been used in [19]. However, path-based techniques suffer from scalability problem, as it enumerates a huge number of paths. The work of [20] somewhat addresses this issue by systematically removing the infeasible paths from the control flow graph.

Implicit path enumeration techniques represent program control flow as linear equations/constraints and formulate the WCET computation problem as maximizing the objective function of an integer linear program (ILP). The solution of the ILP can be derived by any ILP solver (*e.g.* CPLEX [21]). The solution of the ILP contains a quantitative value capturing the WCET of the program and the execution count of different control flow edges. However, the solution of the ILP does not return the exact execution path which leads to the worst-case scenario. The work of [9] first comprehensively combined the abstract interpretation based micro-architectural modeling and the ILP-based path analysis for WCET computation. Moreover, most of the common forms of program flow information (such as infeasible path, loop bound) can easily be encoded as linear constraints and they can be integrated into the WCET formulation (as shown in [5; 22]). Consequently, ILP-based WCET computation has become popular in the research community. Many WCET analyzers currently employ ILP-based (such as Chronos [23], aiT [24]) calculation phase.

Figure 2.3: Overview of a typical WCET analysis framework

Figure 2.4: An example showing ILP-based WCET calculation

Figure 2.3 captures an overview of a typical WCET analysis process. Micro-architectural modeling usually works at the level of basic blocks and computes the WCET of each basic block. Program flow information can be derived by static analysis and some additional flow information can also be given by the user manually. WCET of each basic block and program flow information (loop bound, infeasible path) are used to compute the WCET of the entire program, as shown in Figure 2.3.

#### 2.2 Example

In this section, we shall illustrate the WCET computation by revisiting the example shown in Figure 2.1. We shall use the *implicit path enumeration based* WCET calculation for the illustration.

The example is shown in Figure 2.4(a). Although, WCET analysis is usually carried out on the executable, for the sake of simplicity in the discussion, we shall show the process at the source code level. Control flow graph of the program is shown in Figure 2.4(b).

Let us assume,  $C_B$  denotes the WCET of basic block B derived via micro-architectural modeling. Further assume  $E_{B1B2}$  is the ILP variable which denotes number of times the edge from basic block B1 to basic block B2 is taken in the execution. Therefore, we have the following objective function in the ILP formulation:

Maximize

$$C_S + C_{B2}E_{SB2} + C_{B2}E_{B8B2} + C_{B3}E_{B2B3}$$

+ $C_{B4}E_{B2B4} + C_{B5}E_{B3B5} + C_{B5}E_{B4B5} + C_{B6}E_{B5B6}$

+ $C_{B7}E_{B5B7} + C_{B8}E_{B6B8} + C_{B8}E_{B7B8}$

(2.1)

**Representing control flow and loop bound** Only one execution path is taken at a branch. Therefore, we have a set of control flow constraints as shown in Figure 2.4(c). The program in this example contains a loop and for WCET computation, the loop bound must be known. For the example program, the upper bound on the loop iteration is 50. This loop bound can be explicitly specified by the user or it can also be derived through a complex analysis of the program (e.g., using [7]).

**Representing infeasible path** Certain infeasible path informations can be represented as linear constraints and therefore, they can easily be integrated into the ILP-based calculation. Note that both the basic blocks B3 and basic block B5 cannot be present in any feasible execution. This is due to the infeasible condition  $z == 0 \land z < -2$ . Such infeasible paths can be represented as linear constraints as shown in Figure 2.4(c).

An ILP solver (*e.g.* CPLEX) maximizes the objective function (as specified in Equation 2.1) considering all specified constraints to it (Figure 2.4(c)).

#### 2.3 Chapter summary

In this chapter, we have briefly discussed the different steps involved in a typical WCET analysis process. As the work in this dissertation is concentrated towards multi-core architectures, our work mainly revolves around multi-core specific micro-architectural modeling, while keeping the rest of the phases of a WCET analysis framework mostly unchanged.

## **Chapter 3**

# **Literature Review**

In this Chapter, we present an overview of the existing research in both single and multi-core. As the existing research on shared caches are based on the cache analysis in single core, we first start with an overview of cache analysis in single core. Subsequently, we shall discuss the existing research in shared caches and shared buses in multi-core. Finally, we shall give an overview of the existing memory optimization techniques for improving execution time predictability.

#### 3.1 Cache analysis of a single task

Most of the research in cache modeling consider a single level of instruction cache. Among others, abstract interpretation based cache analysis proposed in [9] deserves mention. For analyzing the cache behaviour of a single task, *must* and *may* cache analysis has been proposed in [9]. *Must* and *may* cache analysis categorize memory references as *all-hit* (AH) and *all-miss* (AM) respectively. The memory block corresponding to an AH categorized memory reference is always in cache when accessed. On the other hand, the memory block corresponding to an AM categorized memory reference is never in cache when accessed. *Must* analysis can be used along with virtual inline and virtual unrolling (VIVU) to significantly improve the analysis precision. In VIVU approach, each loop is unrolled once to distinguish the *cold cache misses* at first iteration of the loop. If a memory reference cannot be classified as AH or AM, it is considered *unclassified* (NC). For a *fully timing composable* architecture, an NC categorized memory reference can be considered as a *cache misse* during worst-case computation. The analysis proposed in [9] has later been extended to analyze multi-level non-inclusive instruction caches (in [12]).

Static analysis of data cache timing effects have also been studied (e.g., see [11; 25]). In particular, [11] adapts the abstract interpretation approach for data cache analysis. One of the major difficulties in data cache analysis is the fact that several executions of an instruction can access different data memory addresses and it is difficult to precisely predict the range of data memory addresses accessed by a particular instruction. The work proposed in [26] addresses this concern somewhat by partial unrolling of loops. A recent approach [27] improves over the state-of-the-art data cache analysis by employing a scope based cache state computation. The work in [27] is based on the insight that a data memory reference may access different memory blocks in different iterations of a loop. For each memory block m accessed by a particular load/store instruction and for each loop nesting depth, [27] defines a set of iteration interval (called as *temporal scope*) in which m could be accessed. A temporal scope  $L \mapsto [x, y]$  of memory block m captures that m can only be accessed between iteration x and iteration y of loop L, but m can never be accessed before iteration x and after iteration y of loop L. Such a temporal scope based partitioning is quite useful for data cache analysis, as different memory blocks accessed by a load/store instruction may have totally *disjoint* temporal scopes and therefore, may not conflict in the cache with each other. Once the temporal scopes are computed for each data reference instruction, [27] employs a scope based *persistence* analysis. Such a persistence analysis classifies each memory block accessed by a data reference as persistence (PS) or unclassified (NC) with respect to a loop nesting depth.

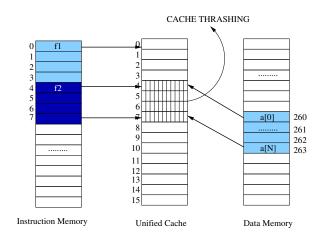

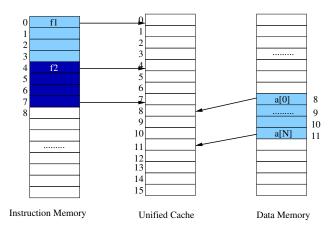

In summary, all existing works on cache modeling focus on either instruction cache or data cache, but not both. Moreover, for cache hierarchies, in most real processors the second-level cache is a unified cache which contains both instruction and data — an issue not considered in existing works. In Chapter 4, we show that the timing unpredictability may arise due to the sharing in unified cache — at the level of different instruction and data memory blocks. In our work (described in Chapter 4), we build on existing works to develop a WCET analyzer which considers separate instruction and data caches in the first level and a unified cache in the second level.

#### **3.2** Inter-task cache conflict analysis

Inter-task cache conflict analysis is required to find an upper bound on cache misses due to preemption. The bound on cache misses (or additional clock cycles) due to preemption is called

cache related preemption delay (CRPD). In last decade, there has been an extensive amount of research to bound the cache related preemption delay (CRPD) [28; 29; 30; 31; 32; 33; 34]. There are three main approaches to statically bound the value of CRPD:

- Analyzing the preempted task ([28; 33]),

- Analyzing the preempting task ([30]), and

- Analyzing both the preempted and the preempting task ([29; 34]).

The analysis of the preempted task revolves around the concept of *useful cache block* (UCB) [28]. A UCB is a block that may be *cached* before preemption and may be *used* later, resulting in a cache hit in the absence of preemption. A *data flow analysis* is applied on the preempted task to statically predict the set of UCBs at each program point. The set of UCBs poses an upper bound on the *additional cache misses* for a single preemption. Recently, [33] has improved the state-of-the-art CRPD analysis [28] by reducing the number of UCBs to consider for CRPD computation. The key idea of [33] is based on the observation that CRPD analysis is always used along with the WCET analysis. Therefore, the technique proposed by [33] considers only those cache misses which were not predicted cache miss by the WCET analysis. In this fashion, [33] may not be able to preserve the over-estimation of CRPD in isolation, however, it can guarantee the over-estimation of the sum of WCET and CRPD.

The analysis of the preempting task is based on the notion of *evicting cache block* (ECB). The set of cache blocks used by the preempting task during its execution is known as ECB. If a cache set is unused by the preempting task, it cannot evict any of the cache blocks used by the preempted task in the respective cache set. Therefore, researchers have proposed to use the set of ECBs for estimating CRPD in [30; 31].

[29] has proposed a precise CRPD analysis approach based on the combination of UCB and ECB. Therefore [29] analyzes both the preempted task (for computing the UCBs) and the preempting task (for computing the ECBs). A UCB may lead to an additional cache miss after preemption only if it might be evicted by an ECB. Such a CRPD analysis framework [29] is more precise than the CRPD analysis based on analyzing either the preempted or the preempting task in isolation. However, the analysis of [29] is based on *direct-mapped* caches. As shown in [34], set-associative caches introduce additional complications in accurately estimating the set of UCBs that can be replaced by a set of ECBs. [34] proposes a CRPD analysis framework for general, set-associative caches.

[32] shows that the precision of CRPD analysis does not only depend on the precision of UCB and ECB, but it also depends on the set of preemption points. The technique proposed by [32] is based on the following insight: if two different preemptions at p and p' may lead to a cache miss of the same memory reference in the preempted task, then we need to consider only one additional cache miss in the preempted task for the set of preemption points  $\{p, p'\}$ . This could be possible, only if the analyzer has the knowledge of both the preemption points p and p'. On the other hand, if we compute the CRPD for p and p' in isolation, it will lead to consider duplicate cache misses for the same memory reference in the preempted task. Computing the CRPD for *all possible set of preemption points* will lead to an exponential slow-down. Therefore, [32] proposes efficient algorithms which account multiple preemption points to improve the precision of *state-of-the-art* CRPD analysis.

In summary, there has been an extensive set of works to estimate CRPD based on UCB and ECB. Several improvements over the state-of-the-art by combining UCB and ECB (*e.g.* [29; 34]) and maintaining the knowledge of multiple preemptions (*e.g.* [32]) have also been proposed in the previous years. However, all of the previous works target a single level cache. On the contrary, we leverage the concept of both UCB and ECB in the context of cache hierarchy in multi-core (described in Chapter 8). To the best of our knowledge, *ours is the first CRPD analysis framework* which targets a cache hierarchy and provides an analysis framework to bound the value of CRPD in the presence of shared caches in multi-core.

#### **3.3** Shared cache analysis

In multi-core systems, tasks in different cores may execute in parallel while sharing memory space in the cache hierarchy. Wei Jhang and Jun Yan [35] were first to introduce the shared cache modeling for software timing analysis. In this work they differentiate a memory block inside some loop or outside any loop. The underlying architecture has two levels of cache where the second level is shared across cores. All memory blocks, which are present in the private cache of a core, do not suffer from the conflicts introduced by the threads running in other cores. Similarly, only L2 cache hits are required to change since L2 cache misses already exploit the worst-case scenario for WCET analysis. Therefore, only L1 cache misses and L2 cache hits are analyzed further to detect possible conflicts introduced by other cores. The analysis works as follows: assume a task T accesses a memory block m and is mapped to cache set C in the L2

cache. Task T' is concurrently running with T in a different core and therefore share the L2 cache with task T. Further assume M' is the set of memory blocks accessed in T' which maps to same cache set C in L2 cache and memory block m was a cache hit in L2 cache ignoring the conflicts from other cores. The classification of memory block m is changed to a L2 cache miss if any of the memory blocks inside the set M' is accessed inside a loop of T'. On the other hand, the classification of memory block m is changed to a *L2 cache hit* if M' contains a single memory block and is accessed outside any loop of T' (since the memory block inside M' can be accessed at most once).

The analysis proposed in [35] has several limitations: first, the approach does not exploit the task dependency. On the other hand, real life embedded applications generally contains multiple tasks and the dependency could be provided through a task graph or message sequence chart [36]. Two dependent tasks can never interfere in the shared resources. Similarly, two different tasks never interfere if their execution times do not overlap. This observation was first made in a recent work proposed in [15]. [15] has proposed an iterative WCRT (Worst Case Response Time) analysis framework for modeling shared cache. Conflicts in shared cache depends on task lifetimes which on other hand depends on shared cache contents of each task. To resolve this dependency, an iterative framework was proposed in [15]. Authors of [15] have also formally proved that their framework always terminates after a finite number of iterations. Secondly, [35] does not employ any additional optimizations for set associative caches. On the other hand, the shared L2 cache is normally made set associative to reduce conflicts. [15] solves this problem with LRU replacement policy. It simply checks, how much more a memory block can grow in a shared cache set in age without conflicts from other cores. Therefore, if number of memory blocks (from the conflicting tasks) mapping to the same cache set is not more than this limit, the corresponding memory block remains to be a cache hit in the shared cache even after conflicts from other cores.

Hardy et al. [37] have proposed a compile time optimization to improve the precision of [35]. The work of [37] performs a compile time analysis to find memory blocks which are used at most once in the program. Since the memory blocks are used only once, they do not heavily affect the performance of the program, however, they might evict some memory blocks from the shared cache which are used heavily by other cores. Therefore, the central idea was to restrict all such memory blocks (used only once) to go into the shared L2 cache.

Existing works on shared caches suffer from overestimating the infeasible inter-core cache

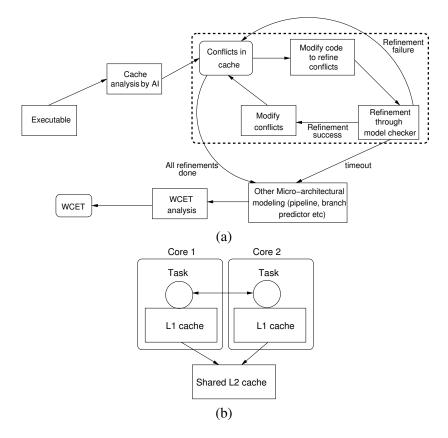

conflicts. In Chapter 5, we propose a novel approach which combines abstract interpretation and model checking for building a *scalable* as well as *precise* WCET analysis framework.

## 3.4 Shared bus modeling